## PHYS 231 – Assignment #6

November 22, 2024

1. (a) Determine the truth table for the combination of NAND gates in the figure below. What binary operation does this combination of NAND gates perform?

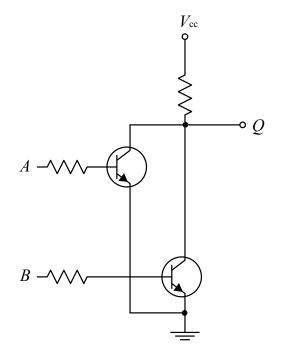

(b) Determine the truth table for the transistor circuit shown in the figure below. What binary operation does this circuit perform? Note that intersecting wires without a dot are *not* connected.

2. Logical theorems and identities:

(a) Prove DeMorgan's theorems:  $\overline{A \cdot B} = \overline{A} + \overline{B}$  and  $\overline{A + B} = \overline{A} \cdot \overline{B}$ . The proofs can consist of simply verifying that the truth tables of the left- and right-hand sides of the equalities are identical.

(b) Show that  $(A + B) \cdot C = A \cdot C + B \cdot C$

- (c) Show that  $A \cdot \overline{A} = 0$

- (d) Show that  $A \cdot A = A$

Again, for (b), (c), and (d) it is sufficient to show that the truth tables for both sides of the expressions are identical.

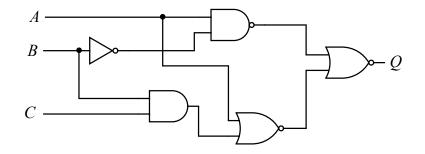

3. Consider the following circuit:

Your task is to design a simpler circuit that will produce the same truth table. You should do this by first writing down a logic expression that represents Q in terms of A, B, and C. Then simplify your expression using some of the identities and theorems that you proved in problem 2. This circuit can be replaced with two gates! Note that wires that intersect without a dot are *not* connected.

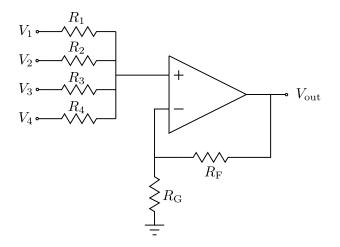

4. The circuit shown below is a 4-bit digital-to-analog converter (DAC). It takes a digital input like 1001, for example, and outputs the corresponding analog voltage.

(a) Show that the output of the op-amp circuit is given by:

$$V_{\text{out}} = \left(1 + \frac{R_{\text{F}}}{R_{\text{G}}}\right) \left[\sum_{j=1}^{N} \frac{1}{R_j}\right]^{-1} \sum_{j=1}^{N} \frac{V_j}{R_j}$$

where in this particular example N = 4. *Hint*: Make use of the fact that the op-amp golden rule for currents requires that  $\sum_{j=1}^{N} I_j = 0$  where  $I_j$  is the current in resistor  $R_j$ .

(b) Now suppose that  $R_1 = 10 \text{ k}\Omega$ ,  $R_2 = 5 \text{ k}\Omega$ ,  $R_3 = 2.5 \text{ k}\Omega$ ,  $R_4 = 1.25 \text{ k}\Omega$ ,  $R_F = 20 \text{ k}\Omega$ , and  $R_G = 10 \text{ k}\Omega$ . What would be the output for the following inputs?

$$(V_4, V_3, V_2, V_1) = (0, 0, 0, 0) V$$

= (0, 0, 0, 5) V

= (0, 0, 5, 0) V

= (0, 0, 5, 5) V

= (0, 0, 5, 5) V

= (0, 5, 0, 0) V

= (0, 5, 5, 0) V

= (0, 5, 5, 5) V

= (5, 0, 0, 0) V

...

= (5, 5, 5, 5) V